Desde hace bastantes años y gracias a TSMC, la tecnología de los transistores evolucionó hacia un nuevo concepto llamado FinFET, el cual se usa actualmente en procesadores de todas las compañías del mundo e incluso en memorias RAM. Pero esta tecnología parece haber llegado a su fin y como tal, todas las CPU del mundo quedarán obsoletas en poco tiempo, dejando paso a un nuevo concepto de transistor más evolucionado: el Nanosheet.

El tamaño de los transistores y la tecnología que emplean para dar paso a la corriente es tan importante o quizá más que el hecho de tener un proceso litográfico de menor tamaño y más preciso, si no, que se lo digan a Intel con sus 14 nm y sus consecuentes mejoras hasta los 14 nm ++.

La litografía determina cuantos transistores pueden entrar perfectamente grabados por milímetro cuadrado, pero no determina las ventajas eléctricas del mismo. Por lo tanto son un tándem que cada fabricante tiene que determinar para dar vida a los sucesivos chips en las obleas.

La longitud de los gate es determinante para el rendimiento

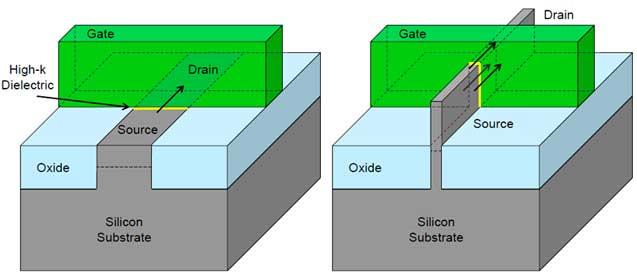

Como todos sabemos, un transistor tiene una simple y determinante función básica: apagarse o encenderse, donde se le conceden dos estados acorde a esta función: encendido o apagado. Para lograrlo el transistor tiene que tener unas medidas en el gate que permiten o cortan el paso de corriente a través de él.

Una de estas medidas es la conocida como longitud del gate. Una menor longitud permite una mayor precisión en el control de la corriente y al mismo tiempo permite más transistores por mm2, pero ser demasiado agresivo con este parámetro puede hacer que el rendimiento empeore.

Por ello, los fabricantes encontraron otro método para seguir mejorando los transistores, el llamado pitch to shrink, es decir, el paso de contacto del transistor, algo que Intel llevó al extremo con sus 14 nm ++ y que ha resultado ser efectivo hasta la llegada de sus 10 nm.

Pero como todo en esta industria, tiene un límite. Según TSMC, la longitud mínima es de aproximadamente 25 nm, donde de seguir bajando esta cifra el rendimiento del transistor se resiente.

FinFET llegó como el salvador, hasta ahora

La solución llegó de parte de Intel y más tarde con otros modelos de su tecnología que copian el concepto principal Trigate. Con FinFET, cada transistor tiene al menos dos fins y por ello tendrá dos gate de control, mientras que Trigate lleva el concepto un poco más allá e incluye una tercera Gate, amplia la altura vertical de las dos primeras mientras que la tercera es la que ejerce el mayor control del voltaje y en encendido y el apagado.

Con ello, el canal de paso tenía un mayor control, pero surgen otros problemas derivados como el espacio mínimo entre los fins por cada proceso litográfico. Reducir las gates en cada cambio litográfico implica que el espacio para introducir aletas (fins) es cada vez menor.

El problema llega justamente desde el punto de vista del aumento de la altura de las aletas y la disminución del ancho del gate. Si esto no puede seguir avanzando para mantener el control de los estados y el voltaje solo quedaría reducir el número de aletas para seguir avanzando en la reducción de las gates, pero esto tampoco es posible porque se pierde control, entonces ¿cómo piensan los fabricantes mejorar los transistores para seguir avanzando?

La solución llega con los nuevos transistores gate-all-around o GAA (Nanosheet)

Las limitaciones están haciendo a los ingenieros y compañías explorar otras opciones que, como es el caso, en el pasado fueron descartadas por su mayor complejidad.

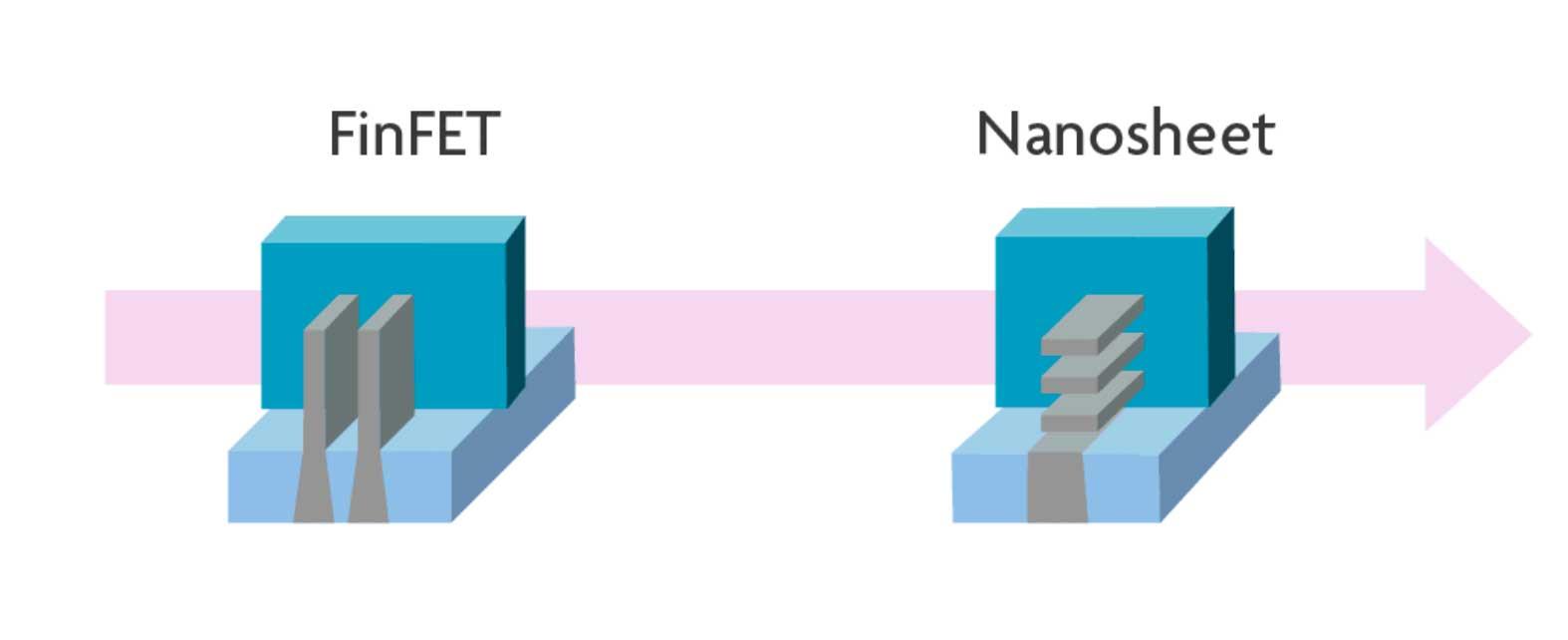

Es el caso de los llamados GAA, donde estos transistores pueden tener fins apilados verticalmente en vez de horizontalmente, lo que comúnmente se le ha denominado Nanosheet, o nanohojas por su similitud a las hojas de un libro o de un taco de folios para impresora.

Este tipo de transistor puede salvar la industria a partir de los 5 nm de TSMC donde a partir de ahora dichos transistores tendrán capas alternas de silicio y SiGe. El problema es que, como hemos comentado, su diseño es más complejo.

Para darles vida, entre las capas de SiGe (compuesto creado entre silicio y germanio) es necesario tener un espaciador interno para el control del voltaje y drenaje del mismo. Este espaciador irá entre el pilar y la gate y define por consecuencia el ancho de dicha gate.

Una vez hecho esto, un grabado primigenio elimina el SiGe sobrante y mediante la deposición de capas atómicas se deposita la gate dieléctrica y el metal de intercambio justo en los espacios entre las nanosheet.

De no lograrse este proceso con la suficiente precisión, el contacto entre el silicio y el SiGe restante que no se ha podido eliminar por completo introducirán en el transistor una tensión poco beneficiosa en un principio. Hablamos por supuesto de tensión de compresión física, ya que se sustituye un material por una serie de elementos que deben ser depositados.

La ventaja de estos transistores nanosheet es que pueden soportar una escalabilidad muy por debajo de las longitudes de gate actuales de 25 nm, donde el límite todavía no se conoce pero sí se sabe que serán inferiores a los 10 nm.

En cualquier caso, hay varias tecnologías que se están desarrollando, pero todas coinciden en que el apilamiento vertical de las capas es el camino a seguir y dejará totalmente obsoletos los transistores actuales, permitiendo un rendimiento mucho más elevado en los procesadores y memorias del futuro.

Te puede interesar: ¿Merece la pena refrigerar por agua el procesador?

[Información e imágenes tomadas de hardzone.es]