La tecnología PCI Express se lleva tiempo utilizando para conectar las tarjetas gráficas y otros periféricos como por ejemplo los discos SSD NVMe. La implementación de la quinta generación de la interfaz se da con la llegada de los procesadores Alder Lake de Intel y los Zen 4 de AMD. Pero la especificación del PCI Express 6.0 ha sido terminada y trae varias mejoras sobre la quinta generación.

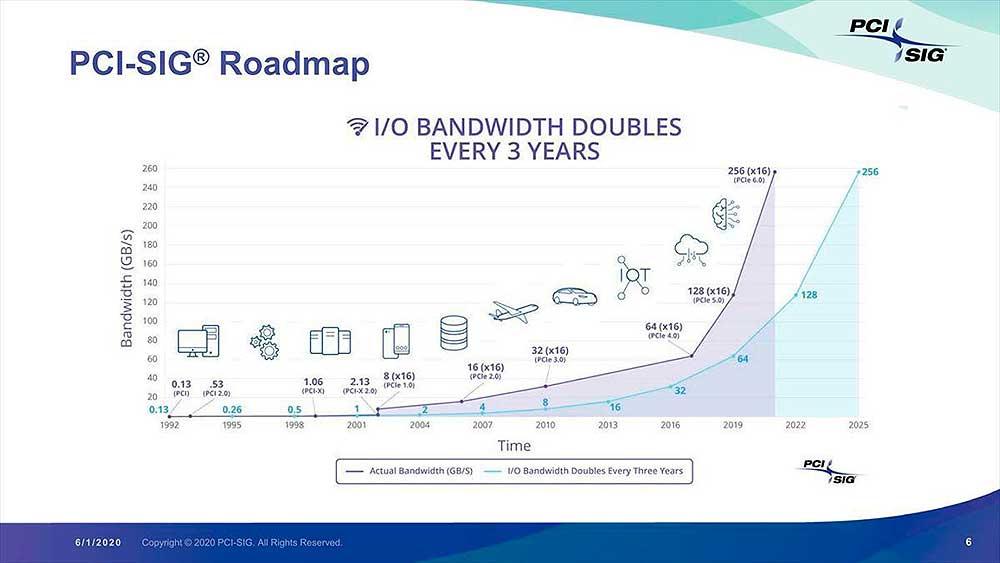

El PCI Express 6.0 sigue de entrada las mismas mejoras que las anteriores generaciones de dicha interfaz, es decir, se basa en duplicar el ancho de banda respecto a la generación anterior. No obstante, en el caso del PCI Express 6.0 se han necesitado cambios profundos en el desarrollo de la sexta generación de esta interfaz.

El ancho de banda del PCI Express 6.0 es de 128 GB/s para una interfaz de 16 líneas., un ancho de banda exageradamente alto para una interfaz de E/S y que es un salto de cuatro veces respecto al actual PCI Express 4.0 que estamos utilizando para las actuales tarjetas gráficas. El salto también significa un salto de los controladores flash SSD NVMe de los 7 – 8 GB/s a los 28 -32 GB/s con el PCI Express 6.0.

Compatibilidad hacia atrás y el problema de la inestabilidad de la señal

La interfaz PCI Express ha sido siempre compatible hacia atrás con versiones anteriores del protocolo, esto significa que podemos conectar una tarjeta PCI Express 1.0 en un slot PCI Express 6.0 y funcionará debido a que el pinaje va a ser exactamente el mismo. Por lo que no es posible aumentar el número de pines para aumentar el ancho de banda sin aumentar la velocidad. ¿La solución? Aumentar la velocidad de reloj a la que funciona la interfaz.

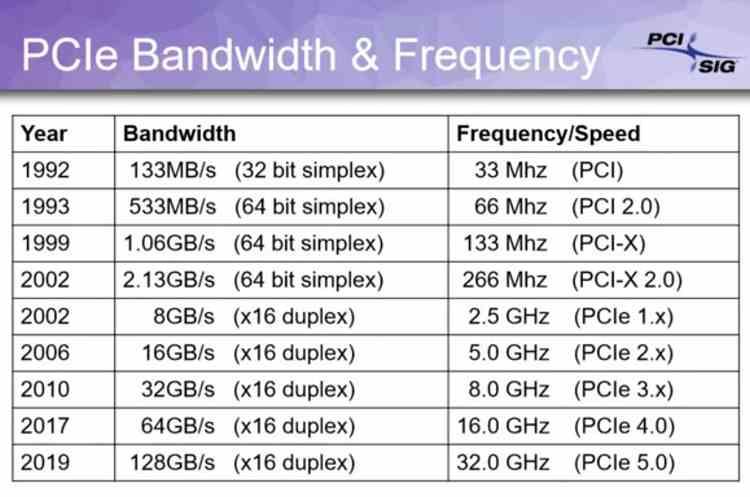

¿El problema con el PCI Express 6.0? A medida que aumentamos la velocidad de reloj de una interfaz esta se va volviendo más inestable con la distancia y después de seis generaciones han tenido que hacer cambios en la interfaz debido a la alta velocidad a la que funciona la interfaz de manera tradicional. Y es que si miráis la tabla que acompaña a estas líneas estamos hablando de una velocidad teórica de 64 GHz, la cual deforma lo suficiente la señal, incluso a la corta distancia a la se encuentran ambos extremos en una interfaz PCI Express.

Esto ha obligado a adoptar una serie de medidas para hacer posible el salto al PCI Express 6.0.

Primera de las mejoras en el PCI Express 6.0, uso de PAM4

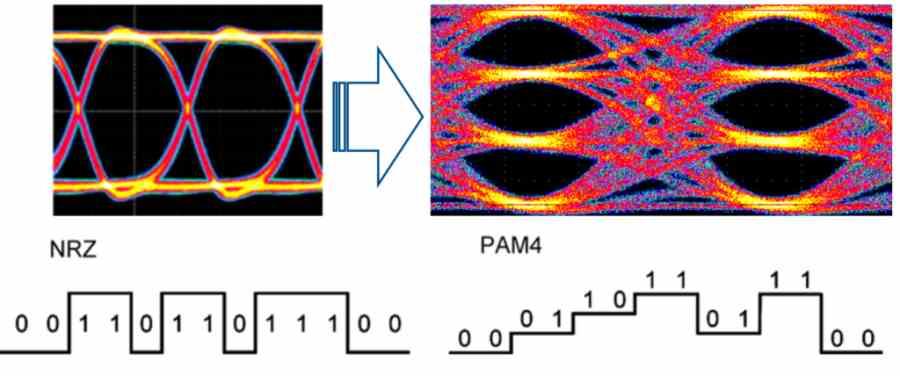

¿Cómo sabe una interfaz externa o interna de un chip si el valor es un 1 o un 0? Pues sencillo, dependiendo del voltaje en el que se transmite la información. Los sistemas binarios se basan en el uso de dos voltajes con la suficiente distancia entre ellos para que la bajada o subida de voltaje haga que la señal no se confunda. En los sistemas analógicos una simple variación en el voltaje supone un cambio en la información. Por ese motivo los ordenadores hablan en binario.

¿Qué tiene que ver esto con el PCI Express 6.0? Dado que no podemos aumentar el ancho de banda porque la señal se distorsiona y tampoco el número de pines por compatibilidad hacia atrás se ha de buscar una solución y esta pasa por el uso codificación PAM4 o Pulse Amplitude Modulation, la cual ya hemos visto en la GDDR6X y no se basa en el uso de dos valores de voltaje sino de 4 valores de voltaje por cada pin. De esta manera podemos codificar los valores 00, 01, 10 y 11 en cada pin. Cuatro valores en total, en vez de los dos valores clásicos que serían 0 o 1.

La solución evita aumentar el ancho de banda y los pines, pero nos adelanta que en el PCI Express 7.0 ya no será posible desde los métodos convencionales. Quizás veamos el uso de fotónica y de interfaces ópticas, pero con las mejoras del PCI Express 6.0 recién salidas del horno, mejor tener paciencia con su sucesor.

Cambios en el sistema de paquetes

El salto a PAM-4 ha cambiado la forma en la que la interfaz PCI Express 6.0 envía sus paquetes, pese a que es compatible con las generaciones anteriores a base de comunicarse en el tradicional modo PAM-2 o NRZ. La realidad es que el formato PAM-4 no soporta el sistema de paquetes anterior y por tanto el protocolo de comunicación ha cambiado debido a ello.

El primer cambio ha sido el llamado Forward Error Correction o FEC, el cual es el nuevo protocolo para corregir los errores en el envío de los datos. El problema es que el ancho de banda a procesar es tan alto que el FEC añade una enorme latencia al envío de los datos. Para paliar esto en el estándar PCI Express 6.0 se utiliza un tipo de paquete llamado FLIT. Un paquete no es más que un conjunto de bits con un destino en concreto. ¿La latencia de envío de cada FLIT? Depende de la cantidad de líneas de la interfaz, pero cada paquete tiene una latencia de solo 2 ns en un PCI Express 6.0 de 16 líneas, pero llega hasta los 32 ns en una interfaz con una sola línea.

El FEC solo trabaja con tamaños fijos, es por ello que el FLIT tiene un tamaño de 256 bytes por envío. Cada paquete o TLP puede tener un tamaño que va de los 0 bytes a los 4096 bytes y por tanto cada paquete puede estar compuesto por varios FLITS.

Tercera mejora al PCI Express 6.0, consumo variable

El PCI Express 6.0 añade un nuevo estado de bajo consumo bautizado como L0P. Este modo le permite a la interfaz recortar su consumo energético cuando el flujo de datos que se envía es más bajo de los que puede transmitir la interfaz. Para ello varía la velocidad de reloj a la que funciona la interfaz en momentos puntuales de la transmisión de datos, todo ello sin que se produzca una parada que añade latencia a la transmisión de datos.

El problema es que este mecanismo está asociado a los FLITS y al FEC y por tanto al PAM4, lo que se traduce en que solo es posible a utilizar en modo PCI Express 6.0 y no en el resto de modos.

Te puede interesar: Usar un SSD como RAM tiene sentido, pero solo a veces

[Información e imágenes tomadas de hardzone.es]